[:el]

Πράξη Αρχιμήδης ΙΙΙ-Ενίσχυση Ερευνητικών Ομάδων στο ΤΕΙ Κρήτης

Υποέργο 31

Ιεραρχικά Κοινόχρηστα Συστήματα Μνήμης για Ενσωματωμένες Εφαρμογές

Επιστημονικός Υπεύθυνος: Μιλτιάδης Γρμματικάκης

Τμήμα Μηχανικών Πληροφορικής, ΤΕΙ Κρήτης

Εσταυρωμένος

Ηράκλειο, 71004 Κρήτη

Κύρια ερευνητική ομάδα:

Μιλτιάδης Γραμματικάκης – Καθηγητής ΤΕΙ, Γεώργιος Κορνάρος – Καθηγητής εφαρμογών ΤΕΙ, Νίκος Παπαδάκης – Καθηγητής εφαρμογών ΤΕΙ, Νεκτάριος Κοζύρης – Αναπληρωτής Καθηγητής ΕΜΠ, Massimo Conti – Καθηγητής Polytecnico De La Marche, Ancona, Italy

Ομάδα εξωτερικών συνεργατών:

Κωνσταντίνος Νίκας, Αντώνης Παπαγρηγορίου, Πολύδωρος Πετράκης, ΙωάννηςΧριστοφοράκης, Όθωνας Τομουτζόγλου, Δημήτρης Μπακογιάννης, Μαρία Αστρινάκη, Σπυριδάκης Αλέξανδρος, Marcello Coppola, Κωνσταντίνος Χαρτερός

Το έργο αφορά την ανάπτυξη μεθοδολογιών και εργαλείων σχεδίασης καθώς και τη μοντελοποίηση και υλοποίηση σε FPGA ιεραρχικών κοινόχρηστων/κατανεμημένων συστημάτων μνήμης για ενσωματωμένα συστήματα σε τσιπ.

Στόχοι:

Στόχος είναι η δημιουργία νέων καινοτόμων εργαλείων για την πειραματική μελέτη ιεραρχικών κοινόχρηστων συστημάτων μνήμης (μοντελοποίηση σε SystemC/VHDL), καθώς και η υλοποίηση πραγματικών συστημάτων σε τσιπ με κοινόχρηστη μνήμη.Eπιδιώκουμε:

- τη μελέτη της βέλτιστης οργάνωσης μνημών σε επίπεδο συστήματος, μελετώντας μηχανισμούς access schedule and data allocation ενώ παράλληλα ερευνάται η επίδραση της τεχνολογίας διασύνδεσης τους (δίκτυο σε τσιπ) στις επιδόσεις και στην ενέργεια που καταναλώνουν όταν χρησιμοποιούνται,

- την ανάπτυξη πρώιμων ειδικών εργαλείων/βιβλιοθηκών EDA (αυτοματοποίησης σχεδιασμού) για εξερεύνηση μοντέλων ιεραρχίας μνήμης και την αυτόματη σχεδίαση από επίπεδο SystemC σε επίπεδο HDL ιεραρχικών κοινόχρηστων συστημάτων μνήμης για ενσωματωμένα συστήματα.

Πεπραγμένα του υποέργου

Το έργο περιλαμβάνει τη μοντελοποίηση εφαρμογών με βάση νέες προτεινόμενες μακροεντολές τύπου SIMD και στην εξαγωγή συμπερασμάτων σχετικά με ένα ελάχιστο σύνολο μακροεντολών που θα μπορούσε να χρησιμοποιηθεί για να υλοποιηθούν με μεγαλύτερη απόδοση (χρόνος εκτέλεσης, ρυθμο-απόδοση, ενέργεια, ισχύς κ.α.) δύο διαφορετικές εφαρμογές:

- παράλληλοι επιστημονικοί υπολογισμοί που αφορούν παράλληλη επεξεργασία δεδομένων σε πίνακες (Jacobi, Floyd-Warshall και n-body)

- βάσεις δεδομένων με έντονη δραστηριότητα μνήμης (memory-intensive transaction systems).

Επίσης αφορά τη δημιουργία βιβλιοθήκης/περιβάλλοντος λογισμικού σε cycle-approximateSystemC και αντίστοιχου τεχνικού εγχειριδίου χρήσης.Πιο συγκεκριμένα, προτείνεται σύνολο μακροεντολών loadbalancing, barrier, scatter, gather, broadcast) που υποστηρίζονται από το CPU, τη δομή πακέτου και την κοινόχρηστη μνήμη (memory controllerγια τη βελτίωση της απόδοσης των δύο εφαρμογών (scientificcomputations,databasetransactions). Η αντιστοίχιση μακροεντολών σε μικρο-εντολές στους ελεγκτές μνήμης του συστήματος (memory controllers) γίνεται με επέκταση της υπάρχουσας βιβλιοθήκης SystemC που μοντελοποιεί ετερογενή πολυπύρηνα συστήματα (multicore SoCs) και αναφέρεται ως Heterogeneous System-on-Chip (HSoC). Η HSoC βιβλιοθήκη παρέχεται ως free, opensource στο site http://sourceforge.net/p/hsoc

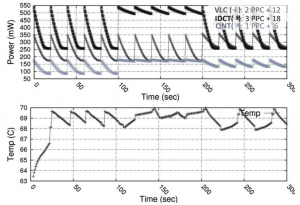

Παράλληλα έγινε ανάπτυξη ετερογενούς island-based δικτύου σε τσιπ με σκοπό τη δημιουργία ενός αυτογνωσιακού συστήματος με δυνατότητα εξισορρόπησης της θερμοκρασίας και της κατανάλωσής του. Για την επίτευξη του στόχου χρησιμοποιήθηκαν τεχνικές δυναμικής αλλαγής συχνότητας (DFS) και συνεχούς παρακολούθησης αισθητήρων θερμότητας και κατανάλωσης ανά κόμβο. Το σύστημα υλοποιήθηκε με την χρήση έξι XilinxML405 FPGAs. Υλοποιήθηκε επιπλέον ένας μηχανισμός που παρακολουθεί τους αισθητήρες και αντιδρά με βάσης ένα αλγόριθμο για κατανεμημένη διαχείριση ενέργειας με σκοπό την ομοιόμορφη κατανομή ενέργειας και θερμοκρασίας σε όλο το σύστημα.

Τέλος έγινε μελέτη των προτεινόμενων μικροεντολών σε επίπεδο συστήματος με βάση τηνεικονική πλατφόρμα HSoC με τη μοντελοποίηση δικτύου σε τσιπ τοπολογίας υπερκύβου(HypercubeNoC) αλλά και σχεδιασμός υλικού (hardware) που υποστηρίζει διαμοιρασμό φορτίου επεξεργαστή και παράλληλες μακροεντολές τύπου broadcast/scatter σε πραγματικό σύστημα με ιεραρχικές μνήμες (ZedboardZ7020 FPGA). Τα παραπάνω πειράματα αποδεικνύουν την υψηλή επιδοση των προτεινόμενων μακροεντολών καθώς και την χαμηλού κόστους (FPGA LUTs) υλοποίηση.

Αποτελέσματα του υποέργου:

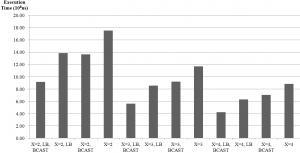

- Όπως φαίνεται στην Εικόνα 1, ο μηχανισμός διαμοιρασμού φορτίου (LB) παρουσιάζει βελτίωση 20% με 29%, ενώ οι μακροεντολές scatter/gather (BCAST) παρουσιάζει μείωση του χρόνου εκτέλεσης κατά 48% με 52%. Αφορά εφαρμογή παράλληλου πολλαπλασιασμού.

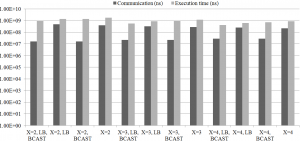

- Στην Εικόνα 2, απεικονίζεται ο χρόνος επικοινωνίας και συγχρονισμού σε σχέση με το συνολικό χρόνο εκτέλεσης της εφαρμογής παράλληλου πολλαπλασιασμού. Με χρήση τουbroadcast/scatter έχουμε βελτίωση για το χρόνο επικοινωνίας κατά τουλάχιστον μία τάξη μεγέθους.

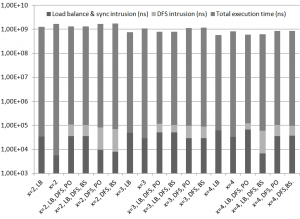

- Στην Εικόνα 3 συνδυάζεται ο μηχανισμός διαμοιρασμού φορτίου επεξεργαστή (LB) με το μηχανισμό δυναμικής αλλαγής συχνότητας (DFS) στα routers του δικτύου σε τσιπ.Η βελτίωση για LB διαμοιρασμού φορτίου (LB) είναι 22% – 32% με κόστος (intrusion) μόλις 0.0003% – 0.0113%, ενώ το το κόστος του DFS είναι 0.003% – 0.009%.

- Στην Εικόνα 4 φαίνεται η προσαρμογή της ισχύος και θερμοκρασίας μέσω DFSpolicy που εφαρμόζεται PPC & MicroBlaze (soft processor) configuration με 6 Xilinx ML405 FPGAs με αισθητήρες ανά κόμβο. Η εφαρμογή αφορά multimedia (αλγορίθμους dithering) και έχει βάση μικροεντολές (kernels) που εκτελούνται σε σύστημα ιεραρχικής μνήμης.

Παραδοτέα του υποέργου:

- Π1/Δ1.1: Τεχνική εργασία (white paper) που προτείνει/επιλέγει ένα σύνολο μακροεντολών και μικροεντολών για τη μοντελοποίηση των δύο εφαρμογών (scientific transaction-based).

- Π2/Δ1.2: Ανάπτυξη κώδικα με μετάφραση από μάκρο- σε μίκρο-εντολές.

- Π3/Δ1.3: Κώδικας C για κατανομή δεδομένων σε μνήμη.

- Π4/Δ2.1: Ανάπτυξη ανοικτού κώδικα SystemC για εικονική πλατφόρμα ιεράρχησης κοινόχρηστης μνήμης. Η βιβλιοθήκη παρέχει γραφική διεπαφή ενώ πρώιμο version δόθηκε στην επιστημονική κοινότητα ως opensource (http://sourceforge.net/p/hsoc)

- Π5/Δ2.2: Σχεδίαση κοινόχρηστης μνήμης σε επίπεδο VHDL και υλοποίηση κοινόχρηστης μνήμης σε FPGA.

- Π6/Δ2.3: Μέτρηση της απόδοση των δύο εφαρμογών.

- Π7/Δ3.1: Αξιοποίηση και Διασπορά. Ιστοσελίδα που παρουσιάζει το έργο.

Εικόνα 1, Χρόνοι εκτέλεσης με LB και BCASTΕικόνα 1, Χρόνοι εκτέλεσης με LB και BCAST

Εικόνα 2, Χρόνος επικοινωνίας και συνολικός χρόνος εκτέλεσης

Εικόνα 3 – Δυναμικός διαμοιρασμός φορτίου και αλλαγή συχνότητας

Εικόνα 4 – Ισχύς και θερμοκρασία σε PPC & MicroBlaze (soft processor)

Δημοσιεύσεις:

- M.D. Grammatikakis, A. Papagrigoriou P. Petrakis, M. Coppola, “System-Level Modeling and SystemC”, Eds. M. Grant, L. Lavagno and I. Markov, EDA for Integrated Circuits Handbook Handbook, Taylor & Francis Group, CRC Press, Chapter 12 (30 pages), 2016, to appear.

- M.D. Grammatikakis, A. Papagrigoriou, P. Petrakis, K. Harteros and G. Kornaros, “Load Balancing, Broadcast, and Scatter Primitives for Efficient Multicore Applications”, in Proc. Workshop on Intelligent Solutions in Embedded Systems, 2015 pp. 23-28.

- I.Christoforakis, O. Tomoutzoglou, D. Bakoyiannis and G. Kornaros, “Dithering-based Power and Thermal Management on FPGA-based Multi-core Embedded Systems”, 13th IEEE/IFIP International Conference on Embedded and Ubiquitous Computing (EUC 2015), Porto, Portugal, 2015, pp. 174-178.

Το έργο υλοποιήθηκε στο πλαίσιο του Επιχειρησιακού Προγράμματος “Εκπαίδευση και Δια Βίου Μάθηση”, Πράξη Αρχιμήδης ΙΙΙ και συγχρηματοδοτήθηκε από την Ευρωπαϊκή Ένωση (Ευρωπαϊκό Κοινωνικό Ταμείο) και εθνικούς πόρους (Εθνικό Στρατηγικό Πλαίσιο Αναφοράς 2007-2013). [:]